16-bit Brent-Kung Adder

Project attribution: Project done nearly solo with help from Ahmed Ghanem and Eric Abraham.

Source: The project’s files are available here.

Short description: 16-bit Brent-Kund Adder Digital IC Design

Technologies: Cadence Virtuoso

What I did: I designed and implemented the schematic and layout of (nearly all) components and of the entire adder.

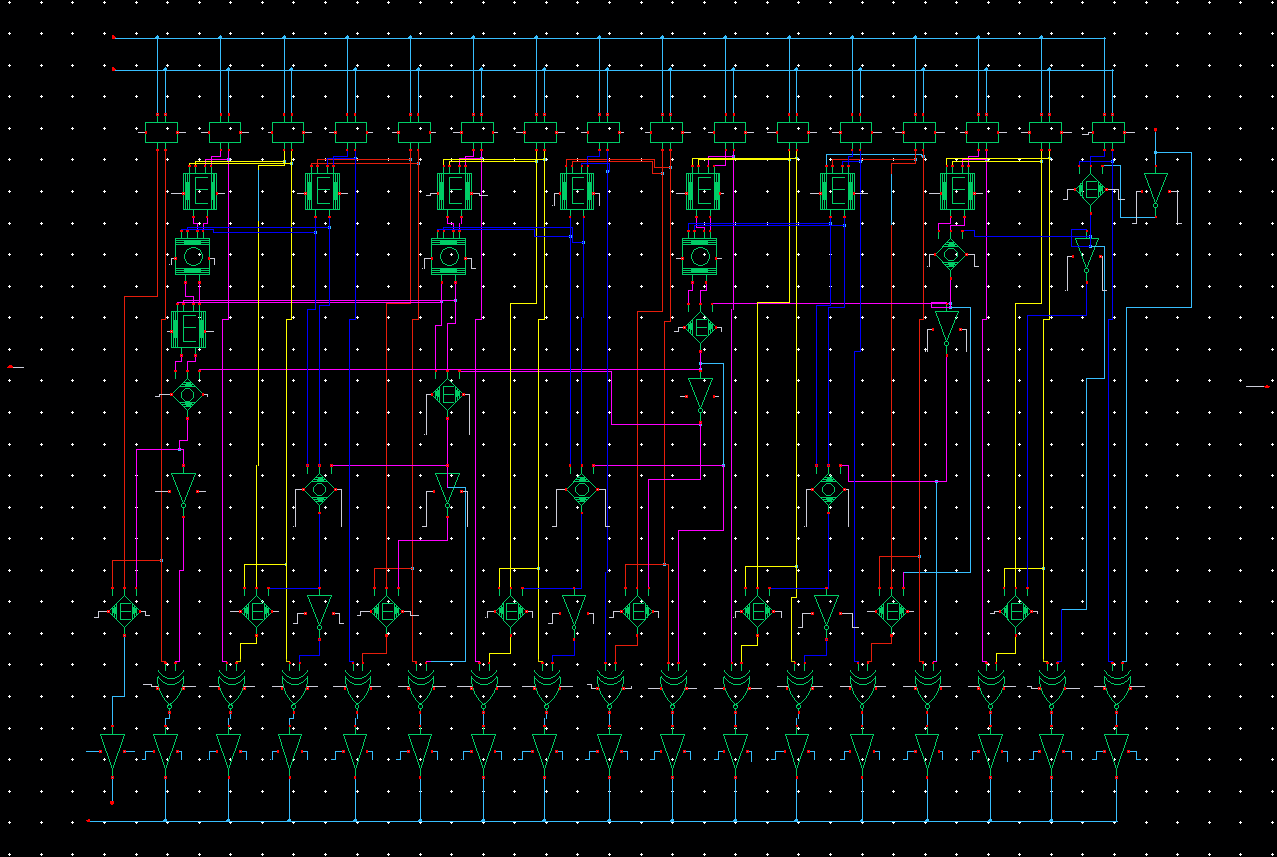

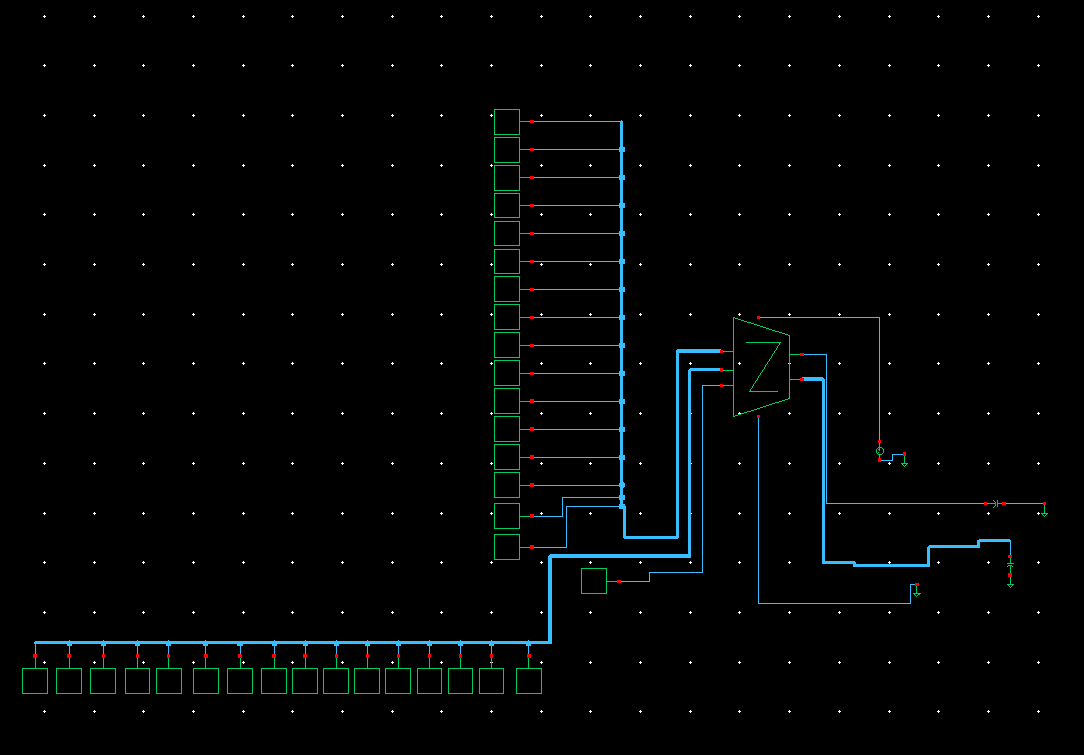

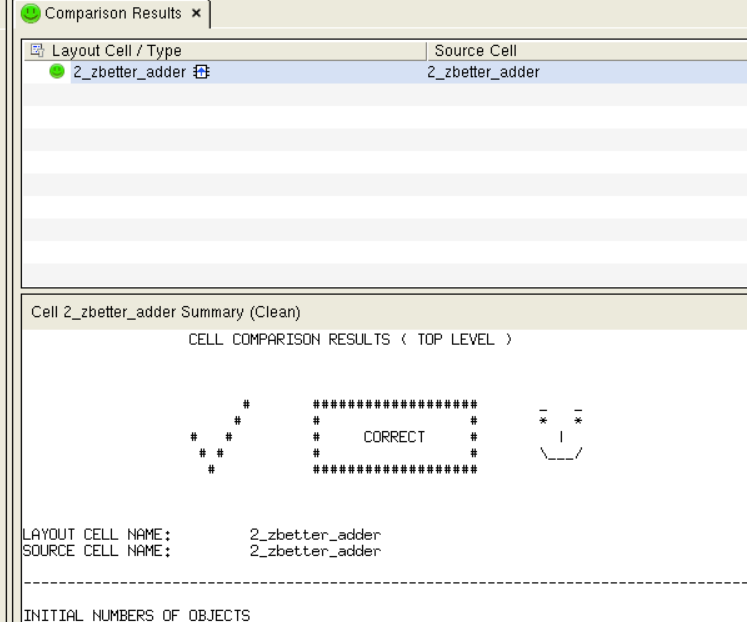

This is a schematic and layout of an IC design that implements a 16-bit full adder following the Brent-Kung architecture. The schematic and layout were made for \(45nm\) CMOS technology, using the industry standard Cadence Virtuoso software.

The adder layout has a total surface of \(177 um^2\) and a maximum critical path delay of \(200 ps\). The layout design leverages custom odd/even black/grey cells and custom preprocessing cells that don’t use other gates underneath. This allows us to reduce the area of their layouts, and consequently the area of the entire adder. You can checkout the schematics and layouts of all components in the images folder of the Github repository.

Adder